Lookup Table: Difference between revisions

m clarify wording |

m fix linking cnf instead of dnf |

||

| Line 1: | Line 1: | ||

Any arbitrary logic formula can always be represented in [[wikipedia: | Any arbitrary logic formula can always be represented in [[wikipedia:Disjunctive_normal_form|https://en.wikipedia.org/wiki/Disjunctive normal form]]. Put in simple terms, this means the output is computed using a single OR-operation, whose inputs are formed by AND gates, which directly use (possibly negated) inputs. Each AND-gate represents a single case where the output is supposed to be ''true''. | ||

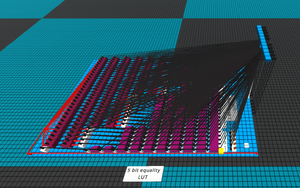

[[File:5BitEqualityLut.png|alt=5 bit equality LUT|thumb|5 bit equality LUT]] | [[File:5BitEqualityLut.png|alt=5 bit equality LUT|thumb|5 bit equality LUT]] | ||

Revision as of 13:00, 6 September 2025

Any arbitrary logic formula can always be represented in https://en.wikipedia.org/wiki/Disjunctive normal form. Put in simple terms, this means the output is computed using a single OR-operation, whose inputs are formed by AND gates, which directly use (possibly negated) inputs. Each AND-gate represents a single case where the output is supposed to be true.

In Logic World, this is referred to as a lookup table (LUT), which is generally implemented by first creating a list of all input states that should lead to a true output. From this list, the LUT can then be constructed quite easily. It consists of multiple relay chains that are simply OR-ed together at the end, where one chain corresponds to one input-assignment that should lead to a truthy output value. The aforementioned relay chains are started by a single NOT-gate whose inputs are all signals that are false in the case where a true output is expected, followed by a set of relays where the top input is expected to be true for such a true result.

Normally, however, it is also necessary to prevent back-propagation of signals by using fast-buffers, meaning each chain requires as many components as there are inputs to account for relays and fast-buffers, along with one NOT-gate if there are any inputs that are supposed to be off.

Complexity

When following the arrangement described above, we can compute the approximate required component count as . If we assume that half of the possible input assignments lead to a true output, the number of chains would be equivalent to . If we factor in, that each chain requires components, the total can be written as . Approximately, this could be written as . In order words, the component count scales exponentially with input size, under the assumption that the amount of true assignment also scales exponentially.

While LUTs tend to become incredibly expensive quite quickly, they are very fast, computing the output in a single tick, regardless of input size. Sometimes, LUTs are the only way of designing a circuit within a predefined, small time constraint (generally in the range of 2-3 ticks).