Tick: Difference between revisions

Appearance

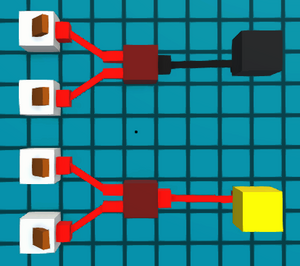

Created page with "{{stub}} A '''tick''' refers to one step of the game's logic simulation. Most components take one tick to update the state of their output after their input changes state. Thus, on some ticks, the state of a component's outputs will be "wrong" compared to the state of its inputs. File:And gate activation delay.png|thumb|A demonstration of two AND gates being activated. The top AND gate has both its inputs active, but its output is not yet active becaus..." |

No edit summary |

||

| Line 6: | Line 6: | ||

[[File:And gate activation delay.png|thumb|A demonstration of two AND gates being activated. The top AND gate has both its inputs active, but its output is not yet active because a delay of 1 tick has not yet passed. The bottom AND gate has had both its inputs active for at least 1 tick, and its output is therefore active.]] | [[File:And gate activation delay.png|thumb|A demonstration of two AND gates being activated. The top AND gate has both its inputs active, but its output is not yet active because a delay of 1 tick has not yet passed. The bottom AND gate has had both its inputs active for at least 1 tick, and its output is therefore active.]] | ||

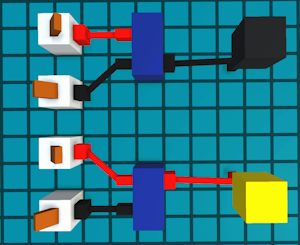

[[File:XOR gate activation delay.png|thumb|A demonstration of two XOR gates being activated. The top XOR gate has one of its inputs active, but its output is not yet active because a delay of 1 tick has not yet passed. The bottom XOR gate has had one of its inputs active for at least 1 tick, and its output is therefore active.]] | |||

Revision as of 22:42, 8 September 2025

A tick refers to one step of the game's logic simulation.

Most components take one tick to update the state of their output after their input changes state. Thus, on some ticks, the state of a component's outputs will be "wrong" compared to the state of its inputs.